丂偙偺儁乕僕偱偼傕偆彮偟俽俢俼俙俵偵偮偄偰孈傝壓偘偰偄偒傑偡丅乮俥俹傗俤俢俷偼傕偆傎偲傫偳栚偵偟側偄偺偱(^^;乯

俽俢俼俙俵偲偄偆偺偼Synchronous Dynamic Ramdam Access Memory偺棯偱摨婜宆俢俼俙俵偲傕屇偽傟偰偄傑偡丅

僋儘僢僋偵摨婜偟偰俢俼俙俵傪摦偐偡偙偲偵傛傝丄俥俹丄俤俢俷側偳偺旕摨婜宆俢俼俙俵傛傝崅懍側摦嶌傪偝偣傞偙偲偑弌棃傑偡丅

偲偙傠偱傒側偝傫偼屼帺暘偱僷僜僐儞偵儊儌儕傪憹愝偟偨傝丄攧偭偰偄傞偺傪尒偨偙偲偑偁傝傑偡偱偟傚偆偐丠

攧偭偰偄傞偺偼DIMM偲屇偽傟傞儃乕僪偺忋偵丄側偵傗傜偘偠偘偠傒偨偄側崟偄怓偺巐妏偔偰嬧怓偺懌偺惗偊偨暔懱偑嵹偭偰偄傞偲巚偄傑偡偑丄偦傟偺堦屄堦屄偑俽俢俼俙俵偺僠僢僾側偺偱偡丅

偁偺彫偝偄暔懱堦屄偺拞偵怴暦偵偟偰壗儁乕僕偩偐偲偄偆忣曬傪偟傑偭偰偍偗傞偺偱偡偐傜丄偐乕側傝偡偛偄偲巚偄傑偣傫偐丠(^^;

丂偝偰SDRAM偵尷偭偨偙偲偱偼偁傝傑偣傫偑儊儌儕偲偄偆傕偺偼僨乕僞傪曐懚偟偰偍偔乛曐懚偟偨僨乕僞傪嶲徠偟偰偔傞丄偲偄偆偙偺俀揰偑栶妱偱偡丅

偱偡偐傜SDRAM偺婎杮揑側摦嶌偲偄偆傕偺偼丄

侾丏儊儌儕偵僨乕僞傪彂偔乮曐懚乯

俀丏儊儌儕偺僨乕僞傪撉傓乮嶲徠乯

偺擇偮偑嵟掅尷偱偒側偄偲峴偗側偄偱偟傚偆丅乮幚嵺偼傕偭偲嵶偐側摦嶌傕偁傝傑偡偑(^^;乯

偐偲偄偭偰偄偒側傝彂偒崬傕偆乛撉傒弌偦偆偲巚偭偰傕偦偆偦偆娙扨偵偼摦偄偰偼偔傟側偄傕偺側偺偱偡偑(^^;

偲偄偆傢偗偱弴孞傝偵SDRAM偺偙偲傪彂偄偰峴偒偨偄偲巚偄傑偡丅

丂SDRAM偼僋儘僢僋怣崋偵摨婜偟偰摦偔偲埲慜偵彂偒傑偟偨偑丄壗偑摨婜偟偰傞偺偐偲偄偆偲丄SDRAM偺僠僢僾偵奜晹偐傜偄傟傞柦椷乮僨乕僞偺撉傒弌偟乛彂偒崬傒側偳乯偲偐僨乕僞側偳偱偡丅

梫偡傞偵SDRAM偵偼僋儘僢僋偵摨婜偟偰僨乕僞傪彂偒崬傫偩傝丄撉傒弌偟偨傝偡傞偙偲偑偱偒傑偡丅乮媡傪尵偊偽僋儘僢僋偵摨婜偟側偄偲偙傟傜偺摦嶌偼偱偒傑偣傫丅乯

偝傜偵偼SDRAM撪晹偺摦嶌傕堦墳偙偺僋儘僢僋偵摨婜偟偰摦偒傑偡丅乮撪晹摦嶌偼摉慠傾僫儘僌揑側摦嶌傕偁傞傫偱堦墳偱偡丅乯

偮傑傝僋儘僢僋偲偼SDRAM傪摦嶌偝偣傞婎弨偺怣崋偱偁傝丄廳梫側怣崋側偺偱偡丅

丂偝偰幚嵺偙偺僋儘僢僋偲偄偆偺偑偳傟傎偳偺廃攇悢偱摦偄偰偄傞偐偲偄偆偲丄椺偊偽SDRAM偺婯奿偺堦偮偱偁傞PC100傪椺偵嫇偘偰傒傞偲丄摦嶌廃攇悢偼100MHz偱偡丅

椺偊偽1Hz偲偄偆偲偙傟偼侾昩娫偵侾夞偺妱崌偱揹埑偑婯懃揑偵忋壓曄摦偡傞偙偲傪帵偟傑偡丅乮偙偺摦偒傪僒僀僋儖偲屇傃傑偡乯

偛壠掚偺揹婥偼俆侽Hz乛俇侽Hz偱摦偒傑偡偐傜侾昩娫偵俆侽夞乛俇侽夞忋壓偵曄摦偡傞偲偄偆偙偲偱偡丅

丂偦傕偦傕偙偺PC100偲偄偆婯奿柤偼侾昩娫偵100M屄偺僨乕僞偺撉傒彂偒偑偱偒傞偲偙傠偐傜偒偰偄傑偡丅SDRAM偼侾夞偺僒僀僋儖偵偮偒僨乕僞偺撉傒彂偒偼堦夞偟偐偱偒側偄偺偱丄PC100亖100MHZ摦嶌偲側傝傑偡丅乮DRDRAM傗DDR SDRAM偼堘偆傫偱偡偑偙傟偼暿偺儁乕僕偱(^^;乯

偱丄100MHz偲偄偆偙偲偼偙偺摦嶌偑侾昩娫偵100M(=100x106)夞婲偙偭偰偄傞偲偄偆偙偲偵側傝傑偡丅

偙傟偑偄偭偨偄偳傟偔傜偄偺帪娫偱婲偙偭偰偄傞偐偲偄偆偲

1昩/100x106夞=10x10-9 昩/侾夞

偲偄偆偙偲偵側傝傑偡丅

偪側傒偵10-9偲偄偆偺偼N乮僫僲乯偲偄偆扨埵偱昞傢偝傟傑偡偺偱丄100Mhz偲偄偆偲僒僀僋儖偼10NS偵堦夞偲偄偆偙偲偵側傝傑偡丅

傑偨PC133偱偡偲133Mhz偱偡偐傜侾僒僀僋儖偑戝懱7.5NS偲偄偆偲偙傠偱偡偹丅

愄偺CM偵傕偁傝傑偟偨偑1NS偲偄偆帪娫偼岝偺懍偝偱偝偊傕傢偢偐30cm偟偐恑傓偙偲偼偱偒側偄帪娫偱偡丅偙傟偩偗彫偝偄帪娫偺扨埵偱SDRAM偼摦偄偰偄傞偺偱偡丅

丂偝偰丄SDRAM偵僨乕僞偺撉傒彂偒傪偝偣傞応崌丄僨乕僞傪撉傓傛偲偐僨乕僞傪彂崬傓傛偲偄偆柦椷傪偟側偄偲摦偒傑偣傫丅

偙偺SDRAM偵偡傞柦椷偺偙偲傪僐儅儞僪偲偄偄傑偡丅

旕摨婜宆偺応崌偼僐儅儞僪傪岲偒彑庤乮偲偄偆偲岅暰戝偒偄偱偡偑(^^;乯側帪娫偵擖傟傞偙偲傕偱偒傞偺偱偡偑丄SDRAM偺応崌偼僋儘僢僋怣崋偺棫偪忋偑傝偺帪偺傒丄僐儅儞僪傪庴偗晅偗偰偔傟傞偺偱偡丅

偱丄傔偱偨偔撉傒彂偒偺柦椷傪SDRAM偵擖傟傞偙偲偵側傞傢偗偱偡偑丄偙偺柦椷偩偗偱偼傕偪傠傫堄恾偟偰傞僨乕僞傪撉傒弌偣傑偣傫丅

帺暘偺梸偟偄僨乕僞傪撉傓乛彂偔傪SDRAM偵偝偣傞偨傔偵偼丄偳偙偺応強偵偁傞儊儌儕僙儖偺僨乕僞傪撉傒乛彂偒偵峴偗偽偄偄偐傕儊儌儕偵嫵偊偰偁偘側偗傟偽摉慠偩傔偱偡傛偹(^^;

偲偄偆傢偗偱師偼偳偙偺儊儌儕僙儖傪撉傒乛彂偒偵峴偔偐乮偙偺応強偺偙偲傪傾僪儗僗偲偄偄傑偡乯偺偍榖偱偡丅

SDRAM乮偵尷傜偢偨偄偰偄偺儊儌儕乯偼偙偺傾僪儗僗偺擖傟曽偑偪傚偭偲摿庩偱偡丅

偲偄偆傢偗偱傾僪儗僗偺巜掕曽朄傪彂偄偰偄偒傑偟傚偆丅

丂椺偲偟偰128Mbit偺DRAM傪忋偘偰偄偒傑偡乮偪側傒偵晛捠僷僜僐儞偺僗儁僢僋昞側偳偵彂偄偰偁傞偺偼byte昞帵偱偡丅1byte=8bit偱昞偝傟丄幚嵺128Mbit偺SDRAM偺儊儌儕堦屄偼16Mbyte偲側傝傑偡丅乯

128Mbit偲偄偆偺偼儊儌儕僙儖偑128M屄偁傞偙偲傪偄偄傑偡丅儊儌儕偺悽奅乮偵尷傜偢俫俢俢偺梕検偲偐乯偱偼俀恑悢傪梡偄傞堊丄128Mbit亖13,421,7728bit偲側傝傑偡丅乮偪側傒偵1Mbit=1024Kbit=1,048,576bit丅俵偼儊僈丄俲偼僉儘偱塸岅寳偺悢帤偵偮偔扨埵偱偡偹(^^;乯

丂偝偰偳偙偺儊儌儕僙儖傪帵偟偰偄傞偺偐傪儊儌儕偵嫵偊傞偺偵丄堦斣娙扨側偺偑128Mbit屄偺僙儖偵弴偵侾丄俀丄俁丒丒丒丒丒侾俀俉俵斣栚傑偱斣崋傪傆偭偰偍偄偰丄偦偺側偐偺壗斣栚偩傛偲偡傞偙偲偩偲巚偄傑偡丅

偑丄偙偺曽朄偩偲13,421,7728偺斣崋傑偱丄偮傑傝俀27(=128Mbit)偲側傝傑偡偐傜27屄偺傾僪儗僗偺悢偑昁梫偲側偭偰偟傑偄傑偡丅乮偔偳偄傛偆偱偡偑儊儌儕偱偼俀恑悢傪巊偄傑偡偺偱(^^;乯

寢壥偲偟偰傾僪儗僗傪擖椡偡傞偝偄偵俀俈寘偲偐昁梫偵側偭偰偟傑偄傑偡偑丄偁傑傝偵悢偑懡偡偓傞堊偙偺曽朄偼尰幚揑偱偼偁傝傑偣傫丅乮梕検偑彮側偐偭偨愄偼傂傚偭偲偟偨傜偙偺曽朄偱傗偭偰偄偨偐傕抦傟傑偣傫偑(^^;乯

丂偝偰丄偱偼偳偆偡傟偽偄偄偐偲偄偄傑偡偲俀師尦丄偮傑傝廲曽岦偲墶曽岦傪傢偗偰倃斣崋亅倄斣崋偲偦傟偧傟斣崋傪偮偗偰偁偘傟偽丄弴斣偵偮偗偰斣崋傪偮偗偰偄偔傛傝傕傾僪儗僗傪尭傜偡偙偲偑偱偒傑偡丅

偲偄偆偙偲偼偨偲偊偽倃偼俀14屄丄倄偼俀13屄(崌寁偼214亊213亖227亖128MBit偱曄傢傜偢)偲俀俈寘偺栺敿暘偱嵪傒傑偡丅

傕偭偲傕堦夞偱擖傟傛偆偲偡傞偲俀俈寘偁傞偺偲曄傢傜側偄偺偱丄幚嵺偼傾僪儗僗傪擇夞偵暘偗偰巜掕偟偰偁偘傑偡丅偙傟偑傾僪儗僗儅儖僠僾儗僋僒偲屇偽傟偰偄傞摦嶌偱偡丅

偦乕偡傟偽倃偲倄偺懡偄曽暘乮崱夞偺応崌偼倃偺侾係寘暘乯偁傟偽傾僪儗僗偺悢偑帠懌傝傑偡偺偱丅

椺偊偽妛峑偱侾妛擭侾侽侽恖偄偨偲偟偰侾斣偐傜侾侽侽斣乮傕偟偔偼侽乣俋俋斣乯傑偱斣崋傪偮偗傞傛傝傕侾侽恖偢偮偵傢偗偰侾侽慻乮傕偟偔偼侽乣俋慻乯偺侾侽斣乮侽乣俋斣乯傑偱偵偟偰偍偄偨曽偑巊偆悢帤偺悢傕彮側偔丄偐偮傢偐傝傗偡偔側傞偲偄偆偍榖偱偡丅

崱屻偼偙偺倃偺偙偲傪儘僂傾僪儗僗(row address)丄倄偺偙偲傪僇儔儉傾僪儗僗(column address)偲尵偄傑偡丅

偱丄幚嵺偵傾僪儗僗傪SDRAM偵嫵偊傞応崌偼偳偆偡傞偐偲偄偄傑偡偲

儘僂傾僪儗僗傪擖傟傞仺僇儔儉傾僪儗僗傪擖傟傞

偲偄偆弴斣偵側偭偰偄傑偡丅

幚嵺偵偼儘僂傾僪儗僗傪偄傟傞偲偒偵偼僠僢僾偺妶惈壔傪峴偄丄僇儔儉傾僪儗僗傪偄傟傞偲偒偵偼撉傒乛彂偒偺偄偢傟偐偺僐儅儞僪傪偄傟偰偄傞偺偱偡偑丅

偲偙偙傑偱棃偰側傫側傫偱偡偑丄俽俢俼俙俵偼倃傾僪儗僗偲倄傾僪儗僗偺懠偵傕偆堦偮僶儞僋偲偄偆嬫愗傝偑偁傝傑偡丅

師偼偙偺僶儞僋偺偙偲偵偮偄偰偪傚偭偲愢柧偟偰傒傑偡丅

丂俽俢俼俙俵偵偼儘僂傾僪儗僗偲僇儔儉傾僪儗僗偺傎偐偵傕偆堦偮僶儞僋偲偄偆奣擮偑偁傝傑偡丅

儘僂傾僪儗僗偑慻丄僇儔儉傾僪儗僗偑弌惾斣崋偲偡傞側傜丄僶儞僋偼妛擭偵憡摉偟傑偡丅

僶儞僋傪暘偗偰偍偔偙偲偵傛傝丄奺僶儞僋偛偲偵摦嶌偑偱偒傞傛偆偵側偭偰偄傞偺偱偡丅

乮侾擭侾慻侾斣偲侾擭俀慻侾斣偼摨帪偵偼屇傋傑偣傫偑丄侾擭侾慻侾斣偲俀擭侾慻侾斣偼摨帪偵屇傇偙偲偑偱偒傞偺偱偡丅乯

丂SDRAM偱偼僶儞僋悢偼係偮乮DDR SDRAM傕堦弿乯丄DRDRAM偱偼俁俀屄偲側偭偰偄傑偡丅

DRDRAM偺僶儞僋悢偑懡偄偺偼丄僶儞僋傪嵶偐偔嬫愗偭偰偍偔偙偲偵傛傝丄SDRAM偲斾傋偰撪晹摦嶌偺崅懍壔傪幚尰偟偰偄傞偨傔偱偡丅乯

丂僷僜僐儞傪帺嶌偟偨偙偲偺偁傞偙偲側傜丄俢俬俵俵偺愢柧偱傛偔CL=2偲偐CL=3偲偐偲偄偆尵梩偑弌偰偔傞偺傪偛懚抦偐偲巚偄傑偡丅

偙偺CL偲偄偆偺偼僇僗儗僀僥儞僔(CAS Latency)偲屇偽傟傞俽俢俼俙俵偺僗儁僢僋偺堦偮側傢偗側傫偱偡偑丄椺偊偽摨偠PC133偺DIMM偱傕俀偲偐俁偲偐偁偭偨傝偟傑偡丅

偍偦傜偔DIMM偺惈擻傪帵偟偰偄傞傫偩傠偆側偀偲偼憐憸拝偔偲巚偄傑偡偑丄偙偺CL偭偰偺偑側傫側偺偐傪偪傚偭偲愢柧偟傑偡丅

SDRAM乮傕偪傠傫DDR SDRAM傗RDRAM偲偐偱傕摨偠乯偱偼丄幚嵺偵撉傒弌偟柦椷傪擖傟偰偐傜忣曬偑弌椡偝傟傞傑偱偵庒姳偺帪娫嵎偑偁傝傑偡丅

僐儅儞僪傪庴偗晅偗偰偐傜僨乕僞傪屇傃弌偟偵峴偭偰弌椡傑偱姰椆偡傞帪娫丄偙傟偺偙偲傪僇僗儗僀僥儞僔偲屇傫偱偄傑偡丅

SDRAM偼僋儘僢僋偵摨婜偟偰偄傑偡偺偱CL=2偲偄偆偲僐儅儞僪傪擖傟偰偐傜僋儘僢僋擇夞屻丄CL=3偲側傞偲僋儘僢僋俁夞屻偐傜僨乕僞偺撉傒弌偟偑偱偒傞傛偆偵側傝傑偡偺偱丄僇僗儗僀僥儞僔偼悢偑彫偝偄傎偳崅懍側儊儌儕偲偄偆偙偲偵側傝傑偡丅

偮傑傝PC133偺CL=2偱偼7.5NSx俀僋儘僢僋側偺偱15NS屻丄CL=3偱偼7.5NSx俁僋儘僢僋側偺偱22.5NS屻丄PC100偺CL=2偱偼10NSx俀僋儘僢僋側偺偱20NS屻偲側傝傑偡丅

僋儘僢僋偵摨婜偟偰傑偡偐傜丄巆擮側偑傜16NS偲偐21NS偲偐僒僀僋儖偱妱傝愗傟側偄拞搑敿抂側帪娫偵偼弌偰偒傑偣傫丅

丂偝偰偙傟偩偗尒傞偲PC133偺CL=3偲PC100偺CL=2偱偼屻幰偺偑憗偄傛偆偵姶偠傑偡偑丄PC133偺曽偑慡懱揑側摦嶌偑懍偄堊乮摦嶌廃攇悢偑崅偄偺偱乯丄僩乕僞儖偱尒傟偽偦傫側偙偲偼側偄偱偡丅

乮幚嵺偺SDRAM偱偼僨乕僞偺撉傒弌偟偼枅搙枅搙侾俛俬俿偱偼側偄偺偱丅乯

偙偺摦嶌傪僶乕僗僩偲屇傃傑偡偑丄偙傟偼傑偨屻偱愢柧偟傑偡丅

丂偝偰侾偮偺傾僪儗僗傪巜掕偟偨偲偒偵堦搙偵弌偰偔傞僨乕僞偺悢偲偄偆偺傕偄傠偄傠偁傝傑偡丅

偙傟偵偮偄偰偼侾bit暘偺傒丄俀bit暘摨帪丄4bit暘摨帪丄俉bit暘摨帪丄侾俇bit暘摨帪丄俁俀bit暘摨帪摍乆梡搑偵傛偭偰暘偐傟傑偡丅

偙偺僨乕僞偺悢偺帠傪僨乕僞暆偲尵偄傑偡丅

偙偺悢偑憹偊傞傎偳堦夞偺撉傒弌偟乛彂偒崬傒柦椷偱埖偊傞僨乕僞検偑憹偊偰偄偒傑偡丅

偦偟偰偙傟偲偼媡偵傾僪儗僗偺悢偼尭偭偰偄偒傑偡丅

僙儖偺悢偼128Mbit偟偐側偄側偄偺偱偡偐傜丄摨偠傾僪儗僗傪帵偟偨偲偒偵弌偰偔傞僨乕僞偺悢偑懡偄傎偳丄儊儌儕僙儖傪巜掕偡傞傾僪儗僗偺悢偼尭偭偰偄偔偺偱偡丅

偮傑傝僨乕僞偺悢倶儘僂傾僪儗僗偺悢倶僇儔儉傾僪儗僗偺悢亊僶儞僋偺悢亖128Mbit偲偄偆寁嶼幃偵側偭偰偄傞偺偱偡丅

丂偨偩偟堦搙偺傾僪儗僗巜掕偱撉傒乛彂偒偱偒傞僨乕僞偺検傪戝偒偔偡傟偽偄偄偐偲偄偆偲偦偆偱傕側偔偰丄僨乕僞偺検傪戝偒偔偡傞偲昁梫側忣曬埲忋偺僨乕僞偺撉傒乛彂偒偑峴傢傟偰寢嬊柍懯偵側傞偐傕偟傟側偄偺偱偡(^^;

椺偊偽擔杮岅慡妏偺侾暥帤偼2byte偺忣曬検偱昞傢偝傟傑偡偑丄偦傟偵4byte(=32bit)偺僨乕僞偺悢偱昞傢偟偰傕2byte偼柍懯偵側傞偩偗偱偡傛偹(^^;

媡偵懡検偺僨乕僞傪堦婥偵昁梫偲偡傞價僨僆僇乕僪側偳偺儊儌儕偼偙偺僨乕僞暆傪憹傗偟偰偄偨傝偲偟傑偡丅

丂偝偰丄俽俢俼俙俵偱偼儘僂傾僪儗僗偲僇儔儉傾僪儗僗傪寛傔偰偁偘偨傜僨乕僞偑弌偰偔傞偙偲偼愭偵墑傋傑偟偨偑丄幚嵺偺僨乕僞偺弌曽偼傕偆彮偟暋嶨偱偡丅

撉傒弌偟偵偟偰傕彂崬傒偵偟偰傕傑偢儘僂傾僪儗僗傪寛傔偰偁偘傞偺偼愭掱彂偄偨捠傝側傫偱偡偑丄偦偺屻僇儔儉傾僪儗僗傪寛傔偰偁偘傞偲偦偺屻偺僇儔儉傾僪儗僗偺僨乕僞傕傑偨弴孞傝偵僨乕僞偑弌偰偒傑偡丅

偙傟傪僶乕僗僩(BURST)摦嶌偲偄偄傑偡丅

偮傑傝侾擭侾慻偺侾斣偺恖傪屇傃弌偟偨傜昁偢俀斣俁斣丒丒丒丒丒偲懕偄偰屇傃弌偝傟傞傛偆側摦嶌傪偡傞偺偱偡丅

楢懕偟偰偔傞僨乕僞偺悢偼偩偄偨偄俀偮乛係偮乛俉偮偺偄偢傟偐偵側偭偰偄傑偡丅

丂偝偰偪傚乕偭偲媄弍幰埲奜偺曽偵偼偪傫傉傫偐傫傉傫偩偲巚偄傑偡偑丄偲傝偁偊偢娙扨偵俽俢俼俙俵偺摦嶌偺愢柧傪偟傑偡丅

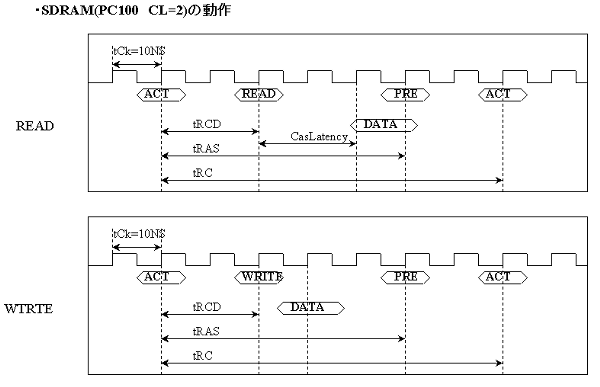

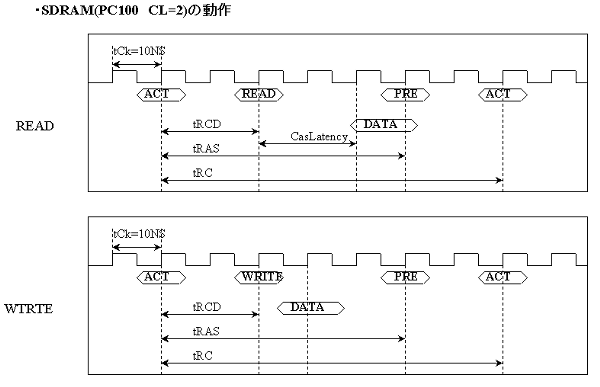

忋恾偵偼俼俤俙俢偲倂俼俬俿俤偲偄偆擇偮偺恾偑偁傝傑偡偑丄俼俤俙俢偲偄偆偺偑僨乕僞偺撉傒弌偟丄倂俼俬俿俤偲偄偆偺偑僨乕僞偺彂偒崬傒偺偲偒偺摦嶌偱偡丅

尒姷傟偸尵梩偑弌偰偒偰傑偡偺偱偪傚偭偲愢柧傪壛偊傑偡丅

丂倲俠俲偲偄偆偺偼侾僒僀僋儖偺帪娫傪昞傢偟偰傑偡丅乮PC100側傜10NS丄PC133側傜7.5NS偱偡偹丅乯

俙俠俿丆俼俤俙俢丆倂俼俬俿俤丆俹俼俤偲偄偆偺偼愭掱弌偰偒偨僐儅儞僪偲偄偆俽俢俼俙俵傪摦偐偡堊偺柦椷偱丄埲壓偺條側堄枴傪帩偪傑偡丅

俙俠俿丂丂丗僠僢僾傪懸婡忬懺偐傜儘僂傾僪儗僗媦傃僶儞僋傾僪儗僗傪庢傝崬傒傑偡

俼俤俙俢丂丗僇儔儉傾僪儗僗媦傃僶儞僋傾僪儗僗傪庢傝崬傫偱丄僨乕僞傪屇傃弌偟傑偡丅

倂俼俬俿俤丗僇儔儉傾僪儗僗媦傃僶儞僋傾僪儗僗傪庢傝崬傫偱丄僨乕僞傪彂崬傒傑偡丅

俹俼俤丂丂丗偡傋偰偺摦嶌傪廔椆偝偣偰懸婡忬懺偵栠傝傑偡丅

丂倲俼俠俢丄倲俼俙俽丄倲俼俠偼僗儁僢僋偲屇偽傟傞傕偺偱丄偙傟偼傑偁奺僐儅儞僪傪楢懕偟偰擖傟傜傟傞栿偱偼側偔丄堦偮僐儅儞僪傪擖傟偨傜師偺僐儅儞僪傪擖傟傞堊偵偼堦掕埲忋偺帪娫偑昁梫偩偲偄偆偙偲偱棟夝偟偰偔偩偝偄丅

偝偰丄傕偆彮偟俽俢俼俙俵偺摦嶌偵偮偄偰傆傟偰偄偒傑偡丅

愭掱儘僂傾僪儗僗偲僇儔儉傾僪儗僗偺愢柧傪偟傑偟偨偑丄俽俢俼俙俵偲偼儔儞僟儉偵傾僋僙僗偱偒傞儊儌儕偺偙偲偱偡偐傜偄偮傕偄偮傕摨偠傾僪儗僗傪屇傃弌偟偨傝偡傞傢偗偱偼偁傝傑偣傫丅

偲偄偆傢偗偱傾僪儗僗傪儔儞僟儉偵摦偐偟偨偲偒偺摦嶌偵怗傟傑偡丅

傑偢僇儔儉傾僪儗僗偺曽偱偡偑丄偙傟偼妱偲帺桼偵摦偐偡偙偲偑偱偒傑偡丅

堦扷儘僂傾僪儗僗傪寛傔偨屻側傜偽丄岲偒彑庤偵僇儔儉傾僪儗僗傪寛傔偰偁偘傞偙偲偑偱偒傞偺偱偡丅

偮傑傝侾擭侾慻傑偱屇傃弌偡偙偲傪寛傔偰偟傑偊偽慻偺拞偺恖偼岲偒側恖傪偦偺傑傑屇傃弌偣傞偺偱偡丅

偮傑傝侾斣偺恖傪屇傫偱丄偦偺屻偱俋斣偺恖傪屇傫偩傝丄俁斣傪屇傫偩傝丄傑偨侾斣傪屇傫偩傝摍乆偑偱偒傞偺偱偡丅

丂偙傟偵懳偟儘僂傾僪儗僗偺曽偼僇儔儉傾僪儗僗偺傛偆偵帺桼偵偼曄偊傜傟傑偣傫丅

堦扷偡傋偰偺摦嶌傪廔偊偰偐傜嵞搙儘僂傾僪儗僗傪擖傟偰傗傞昁梫偑偁傝傑偡丅

侾擭侾慻侾斣偺恖傪屇傫偩屻偵侾擭俁慻侾斣偺恖傪屇傇堊偵偼丄偲傝偁偊偢侾擭侾慻侾斣偺恖傪嫵幒偵傕偳偟丄夵傔偰侾擭俁慻侾斣偲屇傃弌偝側偄偲偄偗側偄偺偱偡丅

丂偝偰崱搙偼攈惗偺偍榖偱偡丅

攈惗偲偄偆偺偼SDRAM側偳偺敿摫懱僠僢僾傪嶌偭偨応崌偳偺婯奿乮PC133偺CL2偲偐PC100偺CL2偲偐乯偑偳傟偔傜偄庢傟偨偐傪偁傜傢偡巜昗偱偡丅

SRDRAM傪嶌傞応崌丄僔儕僐儞婎斅忋偱旝嵶側壛岺乮1um埲壓偺戝偒偝偱壛岺偝傟偰偄傑偡乯傪偡傞偨傔偵傎傫偺偪傚偭偲偟偨偙偲偱丄偙偺攈惗偑戝偒偔曄摦偟偰偟傑偄傑偡丅

偮傑傝PC133CL2偲偟偰攧傜傟傞僠僢僾偲PC100CL2偱攧傜傟傞僠僢僾偵偼丄暿偺愝寁傪偝傟偰偄傞傢偗偱偼側偄偺偱偡丅乮幚嵺偼夵椙傪壛偊偰傛傝崅懍側傕偺偑偨偔偝傫庢傟傞傛偆偵偟偰偄偔傢偗偱偡偑丄婎杮揑偵堦弿偱偡(^^;乯

偙傟偼Athlon傗PentiumIII側偳偺CPU側偳偱1GHz偱摦偔CPU偲800Mhz偱摦偔CPU偱暿偺僠僢僾偲偄偆傢偗偱偼偁傝傑偣傫丄偲偄偆偺偲摨偠偱偡丅

儊乕僇乕偑弌壸慜偵僥僗僩偟偨抜奒偱偙偺僠僢僾偼800MHz側傜摦嶌曐徹偱偒傞丄偙偭偪偼1Ghz傑偱摦嶌曐徹偱偒傞偲偄偆偙偲偱丄慖偽傟偰攧傜傟偰偄傞傢偗偱偡丅

偱偡偑奣偟偰儊乕僇乕偺僥僗僩偼幚巊梡忦審傛傝傕尩偟偄偨傔丄僋儘僢僋傾僢僾側偳偟偰傕摦偄偰偟傑偆応崌偑懡偄傫偱偡偹丅

乮傎偐偵800Mhz偺廀梫偑懡偄偺偵嶌偭偨偺偼1Ghz偱傕摦偔僠僢僾偽偭偐偩丄偲偄偆偲偒偼1GHz偱摦偔僠僢僾傪傢偞傢偞800MHz偱偡丄偲偟偰攧傞偙偲傕偁傝傑偡丅乯

尰嵼攧傜傟偰偄傞DIMM偺婯奿偵偼PC100偺CL2傕PC133偺CL2/CL3偺俁庬椶偑偁傞偲巚偄傑偡丅

CL偲偄偆偺偼僇僗儗僀僥儞僔偺偍榖偺偲偙傠偱愢柧偟偨偲偍傝僨乕僞傪撉傓偲偄偆僐儅儞僪傪SDRAM偺僠僢僾偵梌偊偰偐傜幚嵺偵僨乕僞偑弌偰偔傞傑偱偺帪娫偱偡丅

側偺偱CL3傛傝偼CL2偺偑懍偔僨乕僞偑弌偰偒傑偡丅

PC133偲PC100偼僋儘僢僋偺廃婜傪偁傜傢偟偰偄傑偡偺偱丄PC133偺傎偆偑傛傝崅懍偵摦偔丄偲偄偆偙偲偱偡偹丅

傛偭偰尰忬偺SDRAM偱偼PC133偺CL2偲偄偆僠僢僾偑堦斣崅懍偱摦偔丄偲偄偆偙偲偵側傝傑偡丅乮忋恾傪嶲徠偟偰偔偩偝偄乯

偝偰偱偼偳偺傛偆偵偙偺婯奿偵暘偗傞偺偐偲偄偆偲丄傑偢PC133偲PC100偲偺慖傝暘偗偼僋儘僢僋廃婜偑133MHz偱摦偔偐丄100Mhz偱摦偔偐丄偲偄偆偙偲偱暘偗傜傟傑偡偺偱娙扨偱偡傛偹丅

偱丄摉慠133MHz偱摦偔傕偺偼傛傝掅懍偺100MHz偱傕摦偐偡偙偲偼壜擻偱偡偐傜丄偮傑傝PC133偼PC100偲偟偰傕巊偊傞傢偗偱偡丅

PC133偼PC100偺忋埵屳姺偺婯奿偱偁傞偲偄偊傑偡丅

師偵CL偱偡偑CL133偺CL2偲偄偆偺偼撉傒弌偟僐儅儞僪傪擖傟偰偐傜僋儘僢僋俀夞暘乮15NS乯屻偵偼昁偢僨乕僞偺撉傒弌偟弨旛偑廔傢偭偰偄傑偡丄CL3偱偼僋儘僢僋俁夞暘乮22.5NS乯屻偵偼昁偢僨乕僞偺撉傒弌偟弨旛偑廔傢偭偰偄傑偡丅

偱丄偦傟偧傟僋儘僢僋偵摨婜偟偰僨乕僞傪CPU側偳偵弌椡偡傞傢偗側偺偱偡偑丄偨偲偊偽僨乕僞偺撉傒弌偟弨旛偵15.1NS偐偐偭偨偲偟傑偟丅

偦偆側傞偲僋儘僢僋偺棫偪忋偑傝偱偁傞15Ns乮俀僋儘僢僋屻乯偼夁偓偰偟傑偭偰偄傞偨傔丄偮偓偺22.5NS僲僋儘僢僋僲棫偪忋偑傝偱僨乕僞傪弌椡偡傞偙偲偵側傝傑偡丅

傛偭偰偙偺僠僢僾偼CL3偱摦偔僠僢僾側傝傑偡丅

偮傑傝CL3偲堦岥偵尵偭偰傕僨乕僞偺撉傒弌偟弨旛廔椆傑偱偵15.1NS乣22.5NS偺暆峀偄嵎偑偁傞偺偱偡丅

偙偄偮傕CL2偺DIMM偼CL3偺DIMM偲偟偰傕摉慠巊偊傑偡丅

摨條偵PC100偺CL2偱偼僋儘僢僋俀夞暘乮20NS)屻偵偼昁偢僨乕僞偺撉傒弌偟弨旛廔椆偲側偭偰偄傑偡丅

偙偪傜偺傎偆偼CL3偲偄偆偺偼傑偢尒偐偗傑偣傫偑丄暿偵CL3偱摦偐偟偰傕傕偪傠傫戝忎晇偱偡丅

傑偁丄壗偑偄偄偨偄偺偐偲偄偄傑偡偲PC133CL3偺DIMM偲PC100CL2偺DIMM傪崿嵼偟偰僷僜僐儞偵憹愝偡傞帪偵丄椉曽偲傕抶偄婯奿偺PC100偺CL3偲偐偵崌傢偣傞昁梫偼側偔丄偍偦傜偔PC100偺CL2偱偠傘乕傇傫摦偔偺偱偼側偄偐偲偄偆偙偲偱偡(^^;

乮PC133偺CL3偩偲22.5NS丄PC100偺CL俀偩偲20NS偲慜幰偵崌傢偣側偄偲偩傔側傛偆側婥偑偡傞偲巚偄傑偡偑丄CL2偮傑傝15NS偵娫偵崌偭偰偄側偄偩偗側偺偱丄僨乕僞偺撉傒弌偟弨旛廔椆偼20NS偱廫暘廔傢偭偰偄傞偲巚偄傑偡丅乯

偨偩偟CL3偺愇傪CL2偱巊偆偨傔偵偼儅僓乕儃乕僪偺愝掕偱僇僗儗僀僥儞僔傪曄峏偱偒傞傕偺偱側偄偲偄偗傑偣傫丅

偦傟偲儊乕僇乕偑摦嶌傪曐徹偟偰側偄偺偱丄傕偟僇僗儗僀僥儞僔傪憗傔偰儊儌儕偑夡傟偰偟傑偭偰傕丄巹偵暥嬪傪尵傢側偄偱偔偩偝偄偹(^^;

丂偝偰丄俢俼俙俵偺惈擻傪抦傞忋偱堦偮廳梫側偙偲偑偁傝傑偡丅

偦傟偼彫偝側僶働僣偵擖偭偰偄傞揹壸傪尒偨栚偱敾暿偱偒傞傛偆偵乽憹暆乿傪偟側偄偲峴偗側偄偲偄偆偙偲偱偡丅

偙偺偨傔偵SDRAM偱傕DDRSDRAM偱傕DRDRAM偱傕倃傾僪儗僗偑寛傑偭偰偐傜偙偺憹暆偲偄偆摦嶌傪峴偄傑偡偺偱丄偼偠傔偵僨乕僞偑弌偰偔傞傑偱偺帪娫偼偳偺儊儌儕傕戝懱曄傢傜側偄栿偱偡丅

偙偺偨傔偵DRDRAM偑偄偔傜僶乕僗僩摦嶌傪崅懍壔偟偰傕丄儔儞僟儉偵倃傾僪儗僗傪摦偐偝傟偨傜丄堄枴偑柍偄偲偄偆偙偲偵側傝傑偡丅

偱偼偙偺乽憹暆乿偺僗僺乕僪傪懍偔偱偒側偄偺偱偟傚偆偐丠

偳偙偺儊儌儕儀儞僟乕傕偑傫偽偭偰偄傞偼偢偱偡偑丄側偐側偐弖帪偵憹暆丄偲偄偆傛偆側儊儌儕偼偱偒偰偄傑偣傫偹(^^;

偦傟偵摿偵嬤擭偺愝寁僾儘僙僗乮堦偮偺晹昳傪偙傟偔傜偄偺戝偒偝側傜嶌傟傑偡傛丄偲偄偆儖乕儖乯偺旝嵶壔乮0.18um偲偄偆偺偑崱偺庡棳偱偡丅妋偐敮偺栄堦杮偑100um偩偐10um偩偐掱搙偱偡偐傜憡摉彫偝偄偱偡丅乯偑恑傫偱偄傑偡丅

旝嵶壔偑恑傓偲偄偆偙偲偼僶働僣傕偳傫偳傫彫偝偔側偭偰偒偰偄傞偗偱偡丅

俠亖兠丒俽乛俴

偲偄偆僐儞僨儞僒梕検傪媮傔傞幃傪尒傟偽堦敪偱傢偐傝傑偡偹丅

愝寁儖乕儖偑彫偝偔側傞仺僐儞僨儞僒偺柺愊偑彫偝偔側傞丄偲偄偆偙偲偱偡偺偱(^^;

乮傑丄幚嵺偼桿揹棪乮兠乯偺戝偒側暔幙傪巊偭偨傝丄昞柺愊傪戝偒偔偟偨傝丄偲偄偆偙偲傪偟偰偄傑偡偑偦傟偱傕僶働僣偺梕検偲偟偰偼彫偝偄傫偱偡丅乯