丂傑偢DDR SDRAM偲偄偆偺偼尰嵼偺庡梫儊儌儕偱偁傞SDRAM偺夵椙斉偱偡丅

偳偙傪偳偺傛偆偵夵椙偟偨偐偲偄偆偲丄僨乕僞偺撉傒弌偟乛彂偒弌偟偺晹暘傪夵椙偟偰偄傑偡丅

SDRAM偲偄偆儊儌儕偼僋儘僢僋偵摨婜偟偰摦嶌偡傞偺偱偡偑丄幚嵺偵偼僋儘僢僋偺棫偪忋偑傝乮揹埑偑掅偄儗儀儖偐傜崅偄儗儀儖偵側傞帪乯偺傒偵摨婜偟偰摦嶌偟偰偄傑偟偨丅

偙傟偵懳偟DDR SDRAM偼僨乕僞偺撉傒弌偟乛彂偒弌偟晹暘偺傒僋儘僢僋偺棫偪忋偑傝偲棫偪壓偑傝乮揹埑偑崅偄儗儀儖偐傜掅偄儗儀儖偵側傞帪乯偺椉曽偵摨婜偡傞傛偆偵側偭偰偄傑偡丅

偙偺偨傔尒偐偗忋SDRAM偺攞偺懍搙偱僨乕僞偺撉傒乛彂偒偑偱偒傞偺偱偡丅

乮摦嶌廃攇悢帺懱偼尰嵼偺偲偙傠SDRAM偲曄傢偭偰偄傑偣傫丅乯

丂偙傟偵懳偟DRDRAM偼撈帺偺傾乕僉僥僋僠儍傪梡偄傞偙偲偵傛偭偰僨乕僞偺撉傒乛彂偒偺崅懍壔傪恾偭偰偄傑偡丅

SDRAM傗DDR SDRAM偼僐儅儞僪傪擖傟傞偺偲摨帪偵儘僂傾僪儗僗傑偨偼僇儔儉傾僪儗僗傪擖傟傞偺偱僐儅儞僪擖椡梡偺僺儞乮幚嵺偵DRAM偲偐偲CPU偲偐傪寢傇抂巕丅崟偄暔懱偵偮偄偰偄傞嬧怓偺懌偱偡丅乯偲傾僪儗僗擖椡梡偵僺儞偲椉曽偁傞偺偱偡偑丄DRDRAM偵偼傾僪儗僗擖椡梡偺僺儞偲偄偆傕偺偑偁傝傑偣傫丅

偱偼偳偆傗偭偰傾僪儗僗傪擖椡偡傞偺偐偲偄偄傑偡偲丄僐儅儞僪偲傾僪儗僗傪婔偮偐偵暘夝偟丄僋儘僢僋偵摨婜偝偣偰侾楢偺楢懕偟偨僨乕僞偲偟偰擖椡偡傞偺偱偡丅乮僷働僢僩偲屇偽傟偰偄傑偡乯

偙偺偨傔DRDRAM偼SDRAM偵斾傋偰擖椡梡偺僺儞悢偑彮側偔偰嵪傒丄偦偺傇傫懠偺僺儞偵夞偡偙偲偑偱偒傑偡乮揹尮偲偐乯丅

丂傑偨僶儞僋悢傕DRDRAM偺曽偑嵶偐偔暘偐傟偰偄傑偡丅

乮SDRAM傗DDR SDRAM偑係偮側偺偵懳偟偰DRDRAM偼俁俀屄偲俉攞乯

椺偊偽侾侽侽侽侽恖傪係偮偺妛擭偵暘偗傞傛傝傕丄俁俀偺妛擭偵暘偗偨曽偑丄屇傃弌偟偨偄恖傪憑偟傗偡偄偺偲摨條偵摦嶌偺崅懍壔偵宷偑傞偺偱偡丅

DRDRAM偺摦嶌廃攇悢偑400Mhz偲SDRAM/DDR SDRAM偺傎傏嶰攞(SDRAM偼尰帪揰偱偼133Mhz)偲側偭偰偄傞偙偲偐傜傕丄偦偺撈帺傾乕僉僥僋僠儍偵傛傞崅懍壔偑惉岟偟偰偄傞偲偄偊傞偱偟傚偆丅

乮偨偩偟400Mhz偱摦偄偰偄傞偺偼僀儞僞乕僼僃乕僗晹暘乮Rambus僀儞僞乕僼僃乕僗乯偩偗偱偡丅撪晹僐傾偼SDRAM偲摨偠100Mhz偱摦偄偰偄傑偡丅乯

偪側傒偵Rambus幮帺懱偼DRDRAM傪惗嶻偟偰偄傑偣傫丅

偙偺Rambus幮偼撈帺傾乕僉僥僋僠儍傪摿嫋偲偟偰丄懠偺夛幮乮嶰惎偲偐俶俤俠偲偐搶幣偲偐乯偵儔僀僙儞僗嫙梌偟偰丄偦偺儔僀僙儞僗椏傪庡側廂擖尮偲偟偰偄傑偡丅

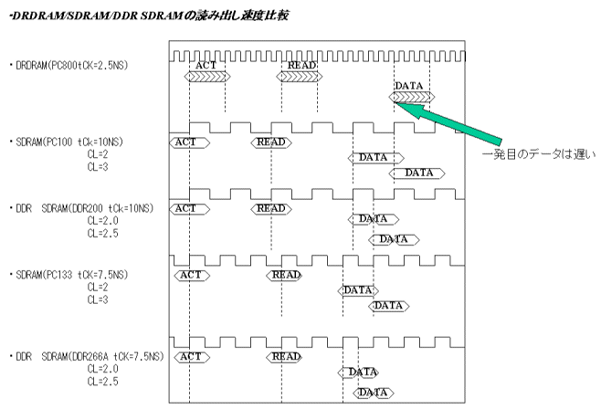

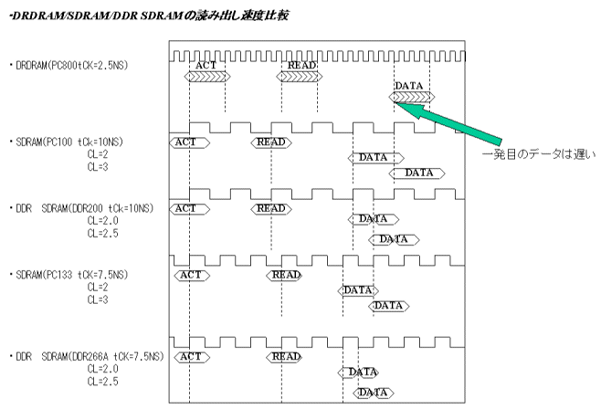

丂偝偰丄偱偼DDR SDRAM偲DRDRAM偑SDRAM偲斾傋偰幚嵺偵偳傟偔傜偄憗偄偺偐傪斾妑偡傞堊偵丄壓恾偺條偵揨傔偰傒傑偟偨丅

偙偺恾偼俙俠俿乮儘僂傾僪儗僗傪庢傝崬傓僐儅儞僪乯偺僋儘僢僋棫偪忋偑傝傪婎揰偵偟偰偍傝丄傑偨堦墳tCK偺弅広偱偼偁偭偰傑偡偺偱丄偳傟偑憗偄偺偐乛抶偄偺偐偼尒偨傑傑偱偡丅

乮傕偭偐偟偨傜娫堘偄偑偁傞偐傕偟傟傑偣傫偑(^^;乯

丂恾傪尒偰偍婥偯偒偐偲巚偄傑偡偑丄椺偵嫇偘偨俆偮乮慡俈庬椶乯偺側偐偱僨乕僞偑弌偼偠傔傞偺偑堦斣抶偄偺偑側傫偲DRDRAM偱偡偹(^^;

偙傟偼壗屘偐偲偄偄傑偡偲DRDRAM偼梮傞SDRAM偺拞偱弎傋偨乭僶乕僗僩摦嶌乭偲乭儔儞僟儉偵僇儔儉傾僪儗僗傪曄峏偟偨応崌乮仼偦偺傑傫傑儔儞僟儉僇儔儉傾僋僙僗摦嶌偲偄偄傑偡乯乭偵偺傒丄偦偺崅懍壔偝傟偨傾乕僉僥僋僠儍偺幚椡傪敪婗偱偒傞偺偱偡丅乮偲偄偄傑偡偐偦偺傛偆偵嶌傜傟偰偄傞傜偟偄丅乯

偙偺偨傔乭僶乕僗僩摦嶌乭偲乭儔儞僟儉僇儔儉傾僋僙僗摦嶌乭偱偼SDRAM偲DDR SDRAM偼DRDRAM偵懢搧懪偪偡傞偙偲偼偱偒傑偣傫丅

偑丄巆擮側偑傜尰嵼偺儊儌儕偺巊梡娐嫬偱偼DRDRAM偺偦偺嫮偝傪敪婗偱偒傞帪偲偄偆偺偑彮側偄偲偄偆偺偑尰忬偺傛偆偱偡丅

偲偄偆傢偗側偺偱DRDRAM偼PC偵忔偭偐傞偲椙偔偰SDRAM暲傒偺惈擻偟偐乮偙偲偵傛偭偨傜SDRAM埲壓乯偱側偄偺偱偡丅

偙偺偙偲偼僀儞僥儖帺懱傕擣傔偰偄傑偡丅intel偺儀儞僠儅乕僋寢壥乮塸岅)

乮僯儏乕僗偩偲僀儞僥儖偑儀儞僠儅乕僋偱Rambus傪掅偔昡壙 偲偐乯

僀儞僥儖偺僠僢僾僙僢僩偱偁傞820偲815偲偺斾妑側偺偱丄傕偟偐偟偨傜尰峴偺僜僼僩偱偼DRDRAM偺嫮傒傪妶偐偣側偄偲偄偆偙偲側偺偐傕偟傟傑偣傫偑偹(^^;

乮偙偺恾傪尒傞尷傝儔儞僟儉儘僂傾僋僙僗摦嶌傪昿斏偵偝傟偨傜丄偳乕偟偰傕SDRAM傛傝抶偔側傝偦偆偱偡偑(^^;乯

偨偩偟尰峴偺i850悽戙偱偼偙偺曈妱偲夵慞偝傟偰偄傞傛偆偱丄偐側傝椙偄僷僼僅乕儅儞僗傪偨偨偒弌偟偰偄傞傛偆偱偡丅

丂儊儌儕傪僷僜僐儞側偳偵憹愝偡傞応崌丄傕偪傠傫扨懱偺傑傑偱偼側偔SDRAM傗DRDRAM偑壗屄偐嵹偭偨斅傪嵎偟崬傒傑偡丅

偙偺斅偺偙偲傪儌僕儏乕儖偲偄偄丄SDRAM傗DDRSDRAM側偳偑忔偭偐偭偰偄傞偺偼DIMM丄DRDRAM偑忔偭偐偭偰偄傞偺偼RIMM偲偄偄傑偡丅

偦偟偰幚嵺偵儌僕儏乕儖偲CPU側偳傪宷偄偱偄傞偺偼儊儌儕僶僗偲屇偽傟傞慄偱丄DIMM偺偙偺慄偺悢偼俇係杮乮偮傑傝64bit偺暆乯丄RIMM偺慄偺悢偼侾俇杮乮偮傑傝16bit乯偱偡丅

傕偪傠傫偙偺僶僗偺暆偑戝偒偄傎偳堦搙偵戝検偺僨乕僞傪CPU偵憲傞偙偲偑偱偒傑偡丅

乮俇係幵慄偲侾俇幵慄偱偼堦搙偵憱傟傞幵偺悢偼摉慠堘偄傑偡傛偹(^^;乯

偙偺嵎偺偍偐偘偱DDR SDRAM偺DIMM偲RIMM偺僨乕僞揮憲懍搙偼摨摍偲偄偆偙偲偵側偭偰偄傞偺偱偡偑丄偝偰丄偱偼側傫偱RIMM偺曽偼儊儌儕僶僗偑16bit暆偟偐側偄偐偲偄偄傑偡偲丄SDRAM偵斾傋偰崅懍昳偩偐傜偱偼側偄偐偲巚傢傟傑偡丅

僒僀僋儖偑2.5NS偲側傞偲攝慄帺懱偵偮偔婑惗梕検傗攝慄掞峈側偳傕柍帇偱偒偢丄偒偪傫偲偙傟埲壓偱側偄偲摦偐側偄丄偲偄偆偙偲偵側傞偺偱偼側偄偐偲丅

偙偺暆偑戝偒偔側傟偽側傞傎偳怣崋偺偽傜偮偒傕戝偒偔側偭偰偄偒傑偡偟偹(^^;

尰嵼偱偼僷僼僅乕儅儞僗夵慞偺偨傔偵儌僕儏乕儖傪擇枃摨帪偵傾僋僙僗偱偒傞傛偆偵偟偨DUAL CAHNNEL偵懳墳偟偨僠僢僾僙僢僩傕弌偰偄傑偡丅

偱偡偑DUAL CHANNEL偵偡傞偲摉慠儊儌儕僶僗暆偼憹偊傑偡偺偱丄憹偊偨偙偲偵傛傞塭嬁偲偐傕戝偒偄傢偗側傫偱偡偑丅

丂傛偔儊儌儕偺惈擻傪乽僨乕僞揮憲懍搙乿偲偄偆傕偺偱帵偟傑偡偑丄偙傟偼DIMM側偄偟RIMM偑侾昩娫偵嵟戝偱偳傟偔傜偄偺僨乕僞傪撉傒弌偣傞偐丄偲偄偆偙偲傪昞傢偟偰偄傑偡丅

偲偄偆傢偗偱娙扨偵寁嶼偟偰傒傑偟傚偆丅

SDRAM偲DDR SDRAM偼DIMM偵偺偭偐偭偰偄傑偡偐傜堦搙偵撉傒弌偣傞僨乕僞偼64bit丅

SDRAM偺PC100婯奿偺応崌丄僨乕僞偼侾僒僀僋儖(=10NS)偵堦屄偟偐弌偣傑偣傫丅

偲偄偆偙偲偼侾昩娫偵100M夞僨乕僞偺撉傒弌偟偑偱偒傑偡丅

DDR SDRAM偺PC1600乮DDR200乯偺応崌丄僨乕僞偼侾僒僀僋儖(=10NS)偵擇偮撉傒弌偣傑偡丅

偲偄偆偙偲偼PC100偺SDRAM偺攞偱偡偐傜100M夞亊俀屄偺僨乕僞偺撉傒弌偟偑偱偒傑偡丅

偮傑傝

SDRAM(PC100) 丗64bit亊100M夞丂丂丂亖 6400Mbit/昩亖 800Mbyte/昩

DDR SDRAM(DDR200)丗64bit亊100M夞倶俀屄亖12800Mbit/昩亖1600Mbyte/昩亖1.6Gbyte/昩

偲側傝傑偡丅

摨條偵PC133偲PC2100乮DDR266)偺応崌偼

SDRAM(PC133) 丗64bit亊133M夞丂丂丂亖 8512Mbit/昩亖1064Mbyte/昩

DDR SDRAM(DDR266A)丗64bit亊133M夞倶俀屄亖17024Mbit/昩亖2128Mbyte/昩亖栺2.1Gbyte/昩

偲側傝傑偡丅

丂偙傟偵懳偟DRDRAM(PC800)偼RIMM偱偡偐傜堦搙偵撉傒弌偣傞僨乕僞偼16bit丅

PC800偺応崌摦嶌僋儘僢僋偼400MHz偱僨乕僞偼DDR SDRAM偲摨偠傛偆偵侾僋儘僢僋偵俀夞弌偰偒傑偡偺偱丄侾昩娫偵400M夞亊俀屄偺僨乕僞偺撉傒弌偟偑偱偒傑偡丅

偲偄偆偙偲偼

DRDRAM(PC800) 丗16bit亊400M夞亊俀屄亖12800Mbit乛昩亖1600Mbyte/昩亖1.6Gbyte/昩

棟榑抣揑偵偼DDR SDRAM(PC1600)偺DIMM偲DRDRAM(PC800)偺RIMM偼摨摍偺惈擻偲偄偆偙偲偵側傝傑偡偹丅

乮偁偔傑偱棟榑抣側傫偱丄幚嵺傎傫偲偵侾昩娫偵偙傫偩偗弌偣傞偺偐偲偄偆偲偐乕側傝媈栤側抣偱偡偑(^^;乯

丂偝偰丄偙偙偱側偤DRDRAM偼柺愊偲儔儞僟儉儘僂摦嶌傪媇惖偵偟偰傑偱僶乕僗僩摦嶌傑偨偼儔儞僟儉僇儔儉摦嶌偵拝栚偟偰崅懍壔傪寁偭偰偄傞偺偐丠偲偄偆媈栤偑偁傞偐偲巚偄傑偡丅

偙傟偵偮偄偰偼僷僜僐儞偺儊儌儕偺娗棟曽朄偵摜傒崬傑側偔偰偼峴偗側偄傫偱偡偑丄娙扨偵偍揱偊偟傑偡偹丅

偦傕偦傕DRDRAM偼intel偵傛偭偰師悽戙偺僷僜僐儞梡偺庡梫儊儌儕偵側傞丄偲偄偆晽偵埵抲偯偗傜傟偰傑偡丅

偮傑傝傕偲傕偲DRDRAM偼僷僜僐儞偺儊儌儕傪庡娽偵偍偄偰嶌傜傟偰偄傞丄偲巚傢傟傞偺偱偡丅

偱丄偙偙偱僷僜僐儞偺儊儌儕偺娗棟側傫偱偡偑丄戝懱埲壓偺傛偆偵側偭偰偄傑偡丅

偦傕偦傕僷僜僐儞偵偼倃傾僪儗僗偲偐倄傾僪儗僗丄壥偰偼僶儞僋側傫偰偄偆奣擮偼偁傝傑偣傫丅

俇係俵俛倷倲倕偺儊儌儕偑偁傞偲偟偨傜壓偐傜弴偵侽丆侾丆俀丒丒丒丒丒俇係俵俛倷倲倕偲娗棟偟偰偄偒傑偡丅

偮傑傝偳偆偄偆帠偐偲偄偄傑偡偲

俹俠偺儊儌儕斣抧丂丂幚嵺偺愇偺斣抧乮倃丆倄乯

丂丂丂丂丂丂丂侽丂丂丂丂丂丂丂丂侽丆丂丂侽

丂丂丂丂丂丂丂侾丂丂丂丂丂丂丂丂侽丆丂丂侾

丂丂丂丂丂丂丂俀丂丂丂丂丂丂丂丂侽丆丂丂俀

丂丂丂丂丂丂丂丒丂丂丂丂丂丂丂丂丒丂丂丂丒

丂丂丂丂丂丂丂丒丂丂丂丂丂丂丂丂丒丂丂丂丒

丂丂丂丂丂丂丂俶丂丂丂丂丂丂丂丂侾丆丂丂侽

丂丂丂丂丂俶亄侾丂丂丂丂丂丂丂丂侾丆丂丂侾

丂丂丂丂丂丂丂丒丂丂丂丂丂丂丂丂丒丂丂丂丒

丂丂丂丂丂丂丂丒丂丂丂丂丂丂丂丂丒丂丂丂丒

丂丂丂丂俇係俵俛丂丂丂丂丂丂俵俙倃丆俵俙倃

偲偄偆晽偵傑偢倄懁偺傾僪儗僗傪懌偟偰偄偔傫偱偡丅

偱丄倄傾僪儗僗偑嵟屻傑偱峴偭偨傜弶傔偰倃傾僪儗僗傪侾恑傔偰傑偨倄傾僪儗僗偺嵟屻傑偱恑傫偱偄偔偲丅

偙偺偨傔DRDRAM偼倄曽岦偺傾僪儗僗偺摦偒偑崅懍偵偱偒傞傛偆偵摿壔偟偰偄傞傢偗側傫偱偡丅

偨偩偟幚嵺偺儊儌儕偵僨乕僞偑彂偒崬傑傟傞嵺丄壓偐傜弴偵婏楉偵彂偒崬傑傟偰偄偔側傫偰偙偲偼傔偭偨偵側偄傫偱偡傛偹(^^;

偩偐傜儀儞僠儅乕僋側偳偱偼丄僶乕僗僩摦嶌偺崅懍壔偺儊儕僢僩傛傝傕儔儞僟儉儘僂摦嶌偺僨儊儕僢僩偑栚棫偭偰偟傑偭偰丄

SDRAM暲傒偐偦傟埲壓偵偟偐尒偊側偐偭偨傝偟傑偡丅

偲傑偁旕忢偵偍偍偞偭傁側傫偱偡偑丄偙傫側棟桼偱DRDRAM偺傾乕僉僥僋僠儍偼寛傔傜傟偨傫偱偼側偄偐偲(^^;